Expansion¶

Pinout Diagrams¶

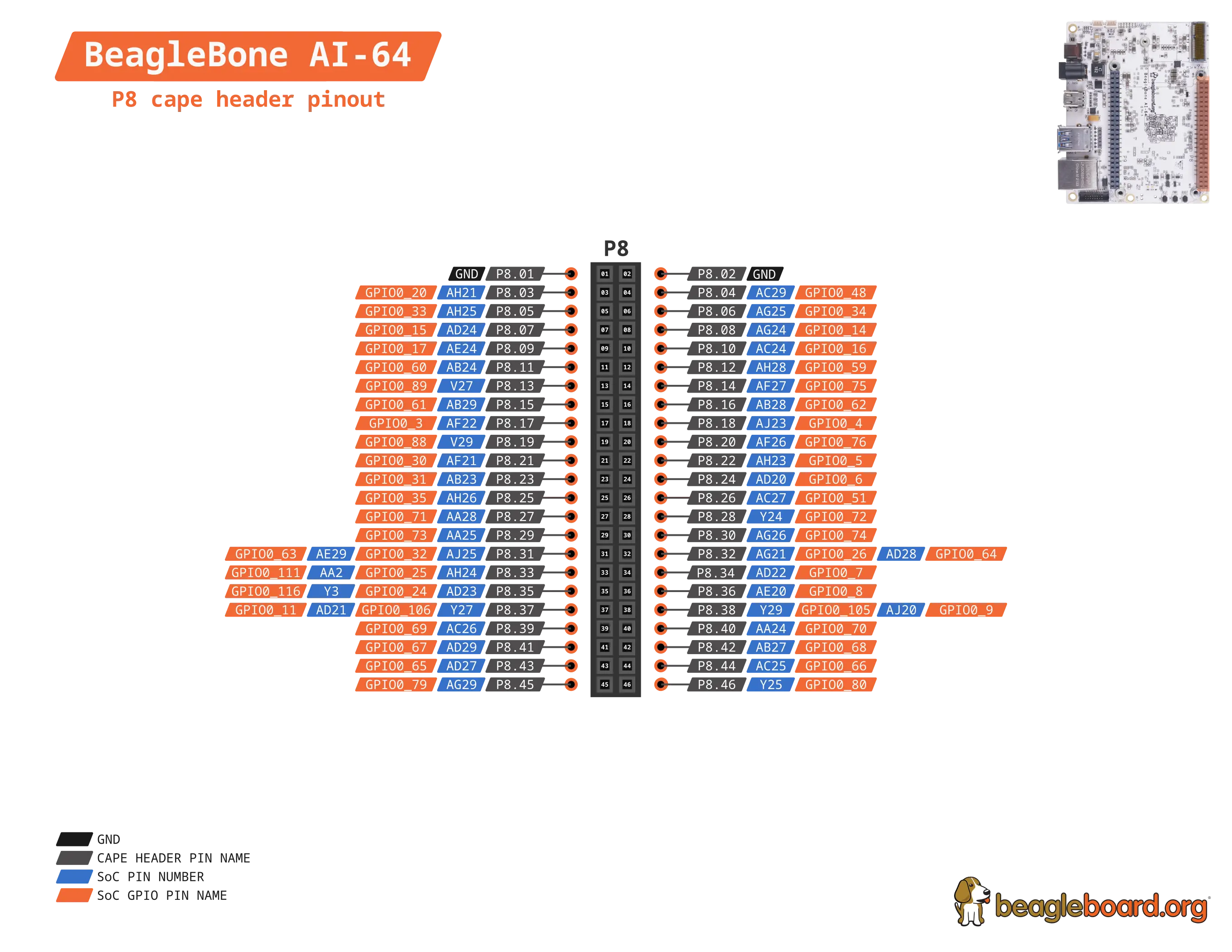

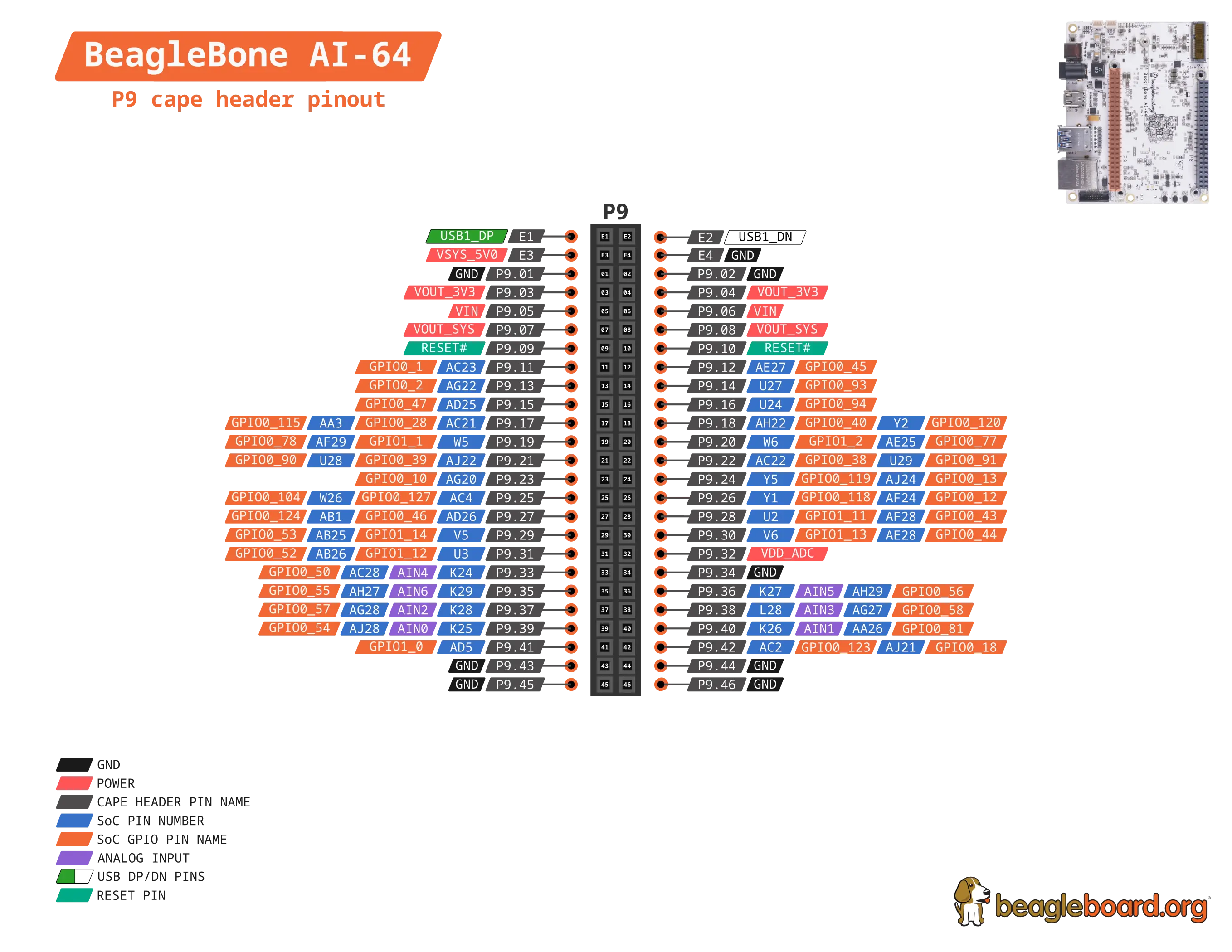

Choose the cape header to see respective pinout diagram.

Cape Header Connectors¶

The cape expansion interface on the board is comprised of two headers P8 (46 pin) & P9 (50 pin). All signals on the expansion headers are 3.3V unless otherwise indicated.

Important

Do not connect 5V logic level signals to these pins or the board will be damaged.

Important

DO NOT APPLY VOLTAGE TO ANY I/O PIN WHEN POWER IS NOT SUPPLIED TO THE BOARD. IT WILL DAMAGE THE PROCESSOR AND VOID THE WARRANTY.

Important

NO PINS ARE TO BE DRIVEN UNTIL AFTER THE SYS_RESET LINE GOES HIGH.

Connector P8¶

The following tables show the pinout of the P8 expansion header. The SW is responsible for setting the default function of each pin. Refer to the processor documentation for more information on these pins and detailed descriptions of all of the pins listed. In some cases there may not be enough signals to complete a group of signals that may be required to implement a total interface.

The column heading is the pin number on the expansion header.

The GPIO row is the expected gpio identifier number in the Linux kernel.

Each row includes the gpiochipX and pinY in the format of X Y. You can use these values to directly control the GPIO pins with the commands shown below.

# to set the GPIO pin state to HIGH

debian@BeagleBone:~$ gpioset X Y=1

# to set the GPIO pin state to LOW

debian@BeagleBone:~$ gpioset X Y=0

For Example:

+---------+----------+

| Pin | P8.03 |

+=========+==========+

| GPIO | 1 20 |

+---------+----------+

Use the commands below for controlling this pin (P8.03) where X = 1 and Y = 20

# to set the GPIO pin state to HIGH

debian@BeagleBone:~$ gpioset 1 20=1

# to set the GPIO pin state to LOW

debian@BeagleBone:~$ gpioset 1 20=0

The BALL row is the pin number on the processor.

The REG row is the offset of the control register for the processor pin.

The MODE # rows are the mode setting for each pin. Setting each mode to align with the mode column will give that function on that pin.

Important

DO NOT APPLY VOLTAGE TO ANY I/O PIN WHEN POWER IS NOT SUPPLIED TO THE BOARD. IT WILL DAMAGE THE PROCESSOR AND VOID THE WARRANTY.

NO PINS ARE TO BE DRIVEN UNTIL AFTER THE SYS_RESET LINE GOES HIGH.

P8.01-P8.02¶

P8.01 |

P8.02 |

|---|---|

GND |

GND |

P8.03-P8.05¶

Pin |

P8.03 |

P8.04 |

P8.05 |

|---|---|---|---|

GPIO |

1 20 |

1 48 |

1 33 |

BALL |

AH21 |

AC29 |

AH25 |

REG |

0x00011C054 |

0x00011C0C4 |

0x00011C088 |

Page |

46 |

30 |

50 |

MODE 0 |

PRG1_PRU0_GPO19 |

PRG0_PRU0_GPO5 |

PRG1_PRU1_GPO12 |

1 |

PRG1_PRU0_GPI19 |

PRG0_PRU0_GPI5 |

PRG1_PRU1_GPI12 |

2 |

PRG1_IEP0_EDC_SYNC_OUT0 |

~ |

PRG1_RGMII2_TD1 |

3 |

PRG1_PWM0_TZ_OUT |

PRG0_PWM3_B2 |

PRG1_PWM1_A0 |

4 |

~ |

~ |

RGMII2_TD1 |

5 |

RMII5_TXD0 |

RMII3_TXD0 |

~ |

6 |

MCAN6_TX |

~ |

MCAN7_TX |

7 |

GPIO0_20 |

GPIO0_48 |

GPIO0_33 |

8 |

~ |

GPMC0_AD0 |

RGMII8_TD1 |

9 |

~ |

~ |

~ |

10 |

VOUT0_EXTPCLKIN |

~ |

VOUT0_DATA12 |

11 |

VPFE0_PCLK |

~ |

~ |

12 |

MCASP4_AFSX |

MCASP0_AXR3 |

MCASP9_AFSX |

13 |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

Bootstrap |

~ |

BOOTMODE2 |

~ |

P8.06-P8.09¶

Pin |

P8.06 |

P8.07 |

P8.08 |

P8.09 |

|---|---|---|---|---|

GPIO |

1 34 |

1 15 |

1 14 |

1 17 |

BALL |

AG25 |

AD24 |

AG24 |

AE24 |

REG |

0x00011C08C |

0x00011C03C |

0x00011C038 |

0x00011C044 |

Page |

51 |

44 |

44 |

45 |

MODE 0 |

PRG1_PRU1_GPO13 |

PRG1_PRU0_GPO14 |

PRG1_PRU0_GPO13 |

PRG1_PRU0_GPO16 |

1 |

PRG1_PRU1_GPI13 |

PRG1_PRU0_GPI14 |

PRG1_PRU0_GPI13 |

PRG1_PRU0_GPI16 |

2 |

PRG1_RGMII2_TD2 |

PRG1_RGMII1_TD3 |

PRG1_RGMII1_TD2 |

PRG1_RGMII1_TXC |

3 |

PRG1_PWM1_B0 |

PRG1_PWM0_A1 |

PRG1_PWM0_B0 |

PRG1_PWM0_A2 |

4 |

RGMII2_TD2 |

RGMII1_TD3 |

RGMII1_TD2 |

RGMII1_TXC |

5 |

~ |

~ |

~ |

~ |

6 |

MCAN7_RX |

MCAN5_RX |

MCAN5_TX |

MCAN6_RX |

7 |

GPIO0_34 |

GPIO0_15 |

GPIO0_14 |

GPIO0_17 |

8 |

RGMII8_TD2 |

~ |

~ |

~ |

9 |

~ |

RGMII7_TD3 |

RGMII7_TD2 |

RGMII7_TXC |

10 |

VOUT0_DATA13 |

VOUT0_DATA19 |

VOUT0_DATA18 |

VOUT0_DATA21 |

11 |

VPFE0_DATA8 |

VPFE0_DATA3 |

VPFE0_DATA2 |

VPFE0_DATA5 |

12 |

MCASP9_AXR0 |

MCASP7_AXR1 |

MCASP7_AXR0 |

MCASP7_AXR3 |

13 |

MCASP4_ACLKR |

~ |

~ |

MCASP7_AFSR |

14 |

~ |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

~ |

P8.10-P8.13¶

Pin |

P8.10 |

P8.11 |

P8.12 |

P8.13 |

|---|---|---|---|---|

GPIO |

1 16 |

1 60 |

1 59 |

1 89 |

BALL |

AC24 |

AB24 |

AH28 |

V27 |

REG |

0x00011C040 |

0x00011C0F4 |

0x00011C0F0 |

0x00011C168 |

Page |

44 |

33 |

33 |

56 |

MODE 0 |

PRG1_PRU0_GPO15 |

PRG0_PRU0_GPO17 |

PRG0_PRU0_GPO16 |

RGMII5_TD1 |

1 |

PRG1_PRU0_GPI15 |

PRG0_PRU0_GPI17 |

PRG0_PRU0_GPI16 |

RMII7_TXD1 |

2 |

PRG1_RGMII1_TX_CTL |

PRG0_IEP0_EDC_SYNC_OUT1 |

PRG0_RGMII1_TXC |

I2C3_SCL |

3 |

PRG1_PWM0_B1 |

PRG0_PWM0_B2 |

PRG0_PWM0_A2 |

~ |

4 |

RGMII1_TX_CTL |

PRG0_ECAP0_SYNC_OUT |

RGMII3_TXC |

VOUT1_DATA4 |

5 |

~ |

~ |

~ |

TRC_DATA2 |

6 |

MCAN6_TX |

~ |

~ |

EHRPWM0_B |

7 |

GPIO0_16 |

GPIO0_60 |

GPIO0_59 |

GPIO0_89 |

8 |

~ |

GPMC0_AD5 |

~ |

GPMC0_A5 |

9 |

RGMII7_TX_CTL |

OBSCLK1 |

~ |

~ |

10 |

VOUT0_DATA20 |

~ |

DSS_FSYNC1 |

~ |

11 |

VPFE0_DATA4 |

~ |

~ |

~ |

12 |

MCASP7_AXR2 |

MCASP0_AXR13 |

MCASP0_AXR12 |

MCASP11_ACLKX |

13 |

MCASP7_ACLKR |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

~ |

Bootstrap |

~ |

BOOTMODE7 |

~ |

~ |

P8.14-P8.16¶

Pin |

P8.14 |

P8.15 |

P8.16 |

|---|---|---|---|

GPIO |

1 75 |

1 61 |

1 62 |

BALL |

AF27 |

AB29 |

AB28 |

REG |

0x00011C130 |

0x00011C0F8 |

0x00011C0FC |

Page |

37 |

33 |

34 |

MODE 0 |

PRG0_PRU1_GPO12 |

PRG0_PRU0_GPO18 |

PRG0_PRU0_GPO19 |

1 |

PRG0_PRU1_GPI12 |

PRG0_PRU0_GPI18 |

PRG0_PRU0_GPI19 |

2 |

PRG0_RGMII2_TD1 |

PRG0_IEP0_EDC_LATCH_IN0 |

PRG0_IEP0_EDC_SYNC_OUT0 |

3 |

PRG0_PWM1_A0 |

PRG0_PWM0_TZ_IN |

PRG0_PWM0_TZ_OUT |

4 |

RGMII4_TD1 |

PRG0_ECAP0_IN_APWM_OUT |

~ |

5 |

~ |

~ |

~ |

6 |

~ |

~ |

~ |

7 |

GPIO0_75 |

GPIO0_61 |

GPIO0_62 |

8 |

~ |

GPMC0_AD6 |

GPMC0_AD7 |

9 |

~ |

~ |

~ |

10 |

~ |

~ |

~ |

11 |

~ |

~ |

~ |

12 |

MCASP1_AXR8 |

MCASP0_AXR14 |

MCASP0_AXR15 |

13 |

~ |

~ |

~ |

14 |

UART8_CTSn |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

P8.17-P8.19¶

Pin |

P8.17 |

P8.18 |

P8.19 |

|---|---|---|---|

GPIO |

1 3 |

1 4 |

1 88 |

BALL |

AF22 |

AJ23 |

V29 |

REG |

0x00011C00C |

0x00011C010 |

0x00011C164 |

Page |

40 |

40 |

57 |

MODE 0 |

PRG1_PRU0_GPO2 |

PRG1_PRU0_GPO3 |

RGMII5_TD2 |

1 |

PRG1_PRU0_GPI2 |

PRG1_PRU0_GPI3 |

UART3_TXD |

2 |

PRG1_RGMII1_RD2 |

PRG1_RGMII1_RD3 |

~ |

3 |

PRG1_PWM2_A0 |

PRG1_PWM3_A2 |

SYNC3_OUT |

4 |

RGMII1_RD2 |

RGMII1_RD3 |

VOUT1_DATA3 |

5 |

RMII1_CRS_DV |

RMII1_RX_ER |

TRC_DATA1 |

6 |

~ |

~ |

EHRPWM0_A |

7 |

GPIO0_3 |

GPIO0_4 |

GPIO0_88 |

8 |

GPMC0_WAIT1 |

GPMC0_DIR |

GPMC0_A4 |

9 |

RGMII7_RD2 |

RGMII7_RD3 |

~ |

10 |

~ |

~ |

~ |

11 |

~ |

~ |

~ |

12 |

MCASP6_AXR0 |

MCASP6_AXR1 |

MCASP10_AXR1 |

13 |

~ |

~ |

~ |

14 |

UART1_RXD |

UART1_TXD |

~ |

Bootstrap |

~ |

~ |

~ |

P8.20-P8.22¶

Pin |

P8.20 |

P8.21 |

P8.22 |

|---|---|---|---|

GPIO |

1 76 |

1 30 |

1 5 |

BALL |

AF26 |

AF21 |

AH23 |

REG |

0x00011C134 |

0x00011C07C |

0x00011C014 |

Page |

37 |

49 |

41 |

MODE 0 |

PRG0_PRU1_GPO13 |

PRG1_PRU1_GPO9 |

PRG1_PRU0_GPO4 |

1 |

PRG0_PRU1_GPI13 |

PRG1_PRU1_GPI9 |

PRG1_PRU0_GPI4 |

2 |

PRG0_RGMII2_TD2 |

PRG1_UART0_RXD |

PRG1_RGMII1_RX_CTL |

3 |

PRG0_PWM1_B0 |

~ |

PRG1_PWM2_B0 |

4 |

RGMII4_TD2 |

SPI6_CS3 |

RGMII1_RX_CTL |

5 |

~ |

RMII6_RXD1 |

RMII1_TXD0 |

6 |

~ |

MCAN8_TX |

~ |

7 |

GPIO0_76 |

GPIO0_30 |

GPIO0_5 |

8 |

~ |

GPMC0_CSn0 |

GPMC0_CSn2 |

9 |

~ |

PRG1_IEP0_EDIO_DATA_IN_OUT30 |

RGMII7_RX_CTL |

10 |

~ |

VOUT0_DATA9 |

~ |

11 |

~ |

~ |

~ |

12 |

MCASP1_AXR9 |

MCASP4_AXR3 |

MCASP6_AXR2 |

13 |

~ |

~ |

MCASP6_ACLKR |

14 |

UART8_RTSn |

~ |

UART2_RXD |

Bootstrap |

~ |

~ |

~ |

P8.23-P8.26¶

Pin |

P8.23 |

P8.24 |

P8.25 |

P8.26 |

|---|---|---|---|---|

GPIO |

1 31 |

1 6 |

1 35 |

1 51 |

BALL |

AB23 |

AD20 |

AH26 |

AC27 |

REG |

0x00011C080 |

0x00011C018 |

0x00011C090 |

0x00011C0D0 |

Page |

50 |

41 |

51 |

31 |

MODE 0 |

PRG1_PRU1_GPO10 |

PRG1_PRU0_GPO5 |

PRG1_PRU1_GPO14 |

PRG0_PRU0_GPO8 |

1 |

PRG1_PRU1_GPI10 |

PRG1_PRU0_GPI5 |

PRG1_PRU1_GPI14 |

PRG0_PRU0_GPI8 |

2 |

PRG1_UART0_TXD |

~ |

PRG1_RGMII2_TD3 |

~ |

3 |

PRG1_PWM2_TZ_IN |

PRG1_PWM3_B2 |

PRG1_PWM1_A1 |

PRG0_PWM2_A1 |

4 |

~ |

~ |

RGMII2_TD3 |

~ |

5 |

RMII6_CRS_DV |

RMII1_TX_EN |

~ |

~ |

6 |

MCAN8_RX |

~ |

MCAN8_TX |

MCAN9_RX |

7 |

GPIO0_31 |

GPIO0_6 |

GPIO0_35 |

GPIO0_51 |

8 |

GPMC0_CLKOUT |

GPMC0_WEn |

RGMII8_TD3 |

GPMC0_AD2 |

9 |

PRG1_IEP0_EDIO_DATA_IN_OUT31 |

~ |

~ |

~ |

10 |

VOUT0_DATA10 |

~ |

VOUT0_DATA14 |

~ |

11 |

GPMC0_FCLK_MUX |

~ |

~ |

~ |

12 |

MCASP5_ACLKX |

MCASP3_AXR0 |

MCASP9_AXR1 |

MCASP0_AXR6 |

13 |

~ |

~ |

MCASP4_AFSR |

~ |

14 |

~ |

~ |

~ |

UART6_RXD |

Bootstrap |

~ |

BOOTMODE0 |

~ |

~ |

P8.27-P8.29¶

Pin |

P8.27 |

P8.28 |

P8.29 |

|---|---|---|---|

GPIO |

1 71 |

1 72 |

1 73 |

BALL |

AA28 |

Y24 |

AA25 |

REG |

0x00011C120 |

0x00011C124 |

0x00011C128 |

Page |

36 |

36 |

36 |

MODE 0 |

PRG0_PRU1_GPO8 |

PRG0_PRU1_GPO9 |

PRG0_PRU1_GPO10 |

1 |

PRG0_PRU1_GPI8 |

PRG0_PRU1_GPI9 |

PRG0_PRU1_GPI10 |

2 |

~ |

PRG0_UART0_RXD |

PRG0_UART0_TXD |

3 |

PRG0_PWM2_TZ_OUT |

~ |

PRG0_PWM2_TZ_IN |

4 |

~ |

SPI3_CS3 |

~ |

5 |

~ |

~ |

~ |

6 |

MCAN11_RX |

PRG0_IEP0_EDIO_DATA_IN_OUT30 |

PRG0_IEP0_EDIO_DATA_IN_OUT31 |

7 |

GPIO0_71 |

GPIO0_72 |

GPIO0_73 |

8 |

GPMC0_AD10 |

GPMC0_AD11 |

GPMC0_AD12 |

9 |

~ |

~ |

CLKOUT |

10 |

~ |

DSS_FSYNC3 |

~ |

11 |

~ |

~ |

~ |

12 |

MCASP1_AFSX |

MCASP1_AXR5 |

MCASP1_AXR6 |

13 |

~ |

~ |

~ |

14 |

~ |

UART8_RXD |

UART8_TXD |

Bootstrap |

~ |

~ |

~ |

P8.30-P8.32¶

Pin |

P8.30 |

P8.31 |

~ |

P8.32 |

~ |

|---|---|---|---|---|---|

GPIO |

1 74 |

1 32 |

1 63 |

1 26 |

1 64 |

BALL |

AG26 |

AJ25 |

AE29 |

AG21 |

AD28 |

REG |

0x00011C12C |

0x00011C084 |

0x00011C100 |

0x00011C06C |

0x00011C104 |

Page |

37 |

50 |

34 |

48 |

34 |

MODE 0 |

PRG0_PRU1_GPO11 |

PRG1_PRU1_GPO11 |

PRG0_PRU1_GPO0 |

PRG1_PRU1_GPO5 |

PRG0_PRU1_GPO1 |

1 |

PRG0_PRU1_GPI11 |

PRG1_PRU1_GPI11 |

PRG0_PRU1_GPI0 |

PRG1_PRU1_GPI5 |

PRG0_PRU1_GPI1 |

2 |

PRG0_RGMII2_TD0 |

PRG1_RGMII2_TD0 |

PRG0_RGMII2_RD0 |

~ |

PRG0_RGMII2_RD1 |

3 |

~ |

~ |

~ |

~ |

~ |

4 |

RGMII4_TD0 |

RGMII2_TD0 |

RGMII4_RD0 |

~ |

RGMII4_RD1 |

5 |

RMII4_TX_EN |

RMII2_TX_EN |

RMII4_RXD0 |

RMII5_TX_EN |

RMII4_RXD1 |

6 |

~ |

~ |

~ |

MCAN6_RX |

~ |

7 |

GPIO0_74 |

GPIO0_32 |

GPIO0_63 |

GPIO0_26 |

GPIO0_64 |

8 |

GPMC0_A26 |

RGMII8_TD0 |

UART4_CTSn |

GPMC0_WPn |

UART4_RTSn |

9 |

~ |

EQEP1_I |

~ |

EQEP1_S |

~ |

10 |

~ |

VOUT0_DATA11 |

~ |

VOUT0_DATA5 |

~ |

11 |

~ |

~ |

~ |

~ |

~ |

12 |

MCASP1_AXR7 |

MCASP9_ACLKX |

MCASP1_AXR0 |

MCASP4_AXR0 |

MCASP1_AXR1 |

13 |

~ |

~ |

~ |

~ |

~ |

14 |

~ |

~ |

UART5_RXD |

TIMER_IO4 |

UART5_TXD |

Bootstrap |

~ |

~ |

~ |

~ |

~ |

P8.33-P8.35¶

Pin |

P8.33 |

~ |

P8.34 |

P8.35 |

~ |

|---|---|---|---|---|---|

GPIO |

1 25 |

1 111 |

1 7 |

1 24 |

1 116 |

BALL |

AH24 |

AA2 |

AD22 |

AD23 |

Y3 |

REG |

0x00011C068 |

0x00011C1C0 |

0x00011C01C |

0x00011C064 |

0x00011C1D4 |

Page |

48 |

67 |

41 |

47 |

67 |

MODE 0 |

PRG1_PRU1_GPO4 |

SPI0_CS0 |

PRG1_PRU0_GPO6 |

PRG1_PRU1_GPO3 |

SPI1_CS0 |

1 |

PRG1_PRU1_GPI4 |

UART0_RTSn |

PRG1_PRU0_GPI6 |

PRG1_PRU1_GPI3 |

UART0_CTSn |

2 |

PRG1_RGMII2_RX_CTL |

~ |

PRG1_RGMII1_RXC |

PRG1_RGMII2_RD3 |

~ |

3 |

PRG1_PWM2_B2 |

~ |

PRG1_PWM3_A1 |

~ |

UART5_RXD |

4 |

RGMII2_RX_CTL |

~ |

RGMII1_RXC |

RGMII2_RD3 |

~ |

5 |

RMII2_TXD0 |

~ |

RMII1_TXD1 |

RMII2_RX_ER |

~ |

6 |

~ |

~ |

AUDIO_EXT_REFCLK0 |

~ |

PRG0_IEP0_EDIO_OUTVALID |

7 |

GPIO0_25 |

GPIO0_111 |

GPIO0_7 |

GPIO0_24 |

GPIO0_116 |

8 |

RGMII8_RX_CTL |

~ |

GPMC0_CSn3 |

RGMII8_RD3 |

PRG0_IEP0_EDC_LATCH_IN0 |

9 |

EQEP1_B |

~ |

RGMII7_RXC |

EQEP1_A |

~ |

10 |

VOUT0_DATA4 |

~ |

~ |

VOUT0_DATA3 |

~ |

11 |

VPFE0_DATA13 |

~ |

~ |

VPFE0_WEN |

~ |

12 |

MCASP8_AXR2 |

~ |

MCASP6_AXR3 |

MCASP8_AXR1 |

~ |

13 |

MCASP8_ACLKR |

~ |

MCASP6_AFSR |

MCASP3_AFSR |

~ |

14 |

TIMER_IO3 |

~ |

UART2_TXD |

TIMER_IO2 |

~ |

Bootstrap |

~ |

~ |

~ |

~ |

~ |

P8.36-P8.38¶

Pin |

P8.36 |

P8.37 |

~ |

P8.38 |

~ |

|---|---|---|---|---|---|

GPIO |

1 8 |

1 106 |

1 11 |

1 105 |

1 9 |

BALL |

AE20 |

Y27 |

AD21 |

Y29 |

AJ20 |

REG |

0x00011C020 |

0x00011C1AC |

0x00011C02C |

0x00011C1A8 |

0x00011C024 |

Page |

42 |

58 |

43 |

58 |

42 |

MODE 0 |

PRG1_PRU0_GPO7 |

RGMII6_RD2 |

PRG1_PRU0_GPO10 |

RGMII6_RD3 |

PRG1_PRU0_GPO8 |

1 |

PRG1_PRU0_GPI7 |

UART4_RTSn |

PRG1_PRU0_GPI10 |

UART4_CTSn |

PRG1_PRU0_GPI8 |

2 |

PRG1_IEP0_EDC_LATCH_IN1 |

~ |

PRG1_UART0_RTSn |

~ |

~ |

3 |

PRG1_PWM3_B1 |

UART5_TXD |

PRG1_PWM2_B1 |

UART5_RXD |

PRG1_PWM2_A1 |

4 |

~ |

~ |

SPI6_CS2 |

CLKOUT |

~ |

5 |

AUDIO_EXT_REFCLK1 |

TRC_DATA19 |

RMII5_CRS_DV |

TRC_DATA18 |

RMII5_RXD0 |

6 |

MCAN4_TX |

EHRPWM5_A |

~ |

EHRPWM_TZn_IN4 |

MCAN4_RX |

7 |

GPIO0_8 |

GPIO0_106 |

GPIO0_11 |

GPIO0_105 |

GPIO0_9 |

8 |

~ |

GPMC0_A22 |

GPMC0_BE0n_CLE |

GPMC0_A21 |

GPMC0_OEn_REn |

9 |

~ |

~ |

PRG1_IEP0_EDIO_DATA_IN_OUT29 |

~ |

~ |

10 |

~ |

~ |

OBSCLK2 |

~ |

VOUT0_DATA22 |

11 |

~ |

~ |

~ |

~ |

~ |

12 |

MCASP3_AXR1 |

MCASP11_AXR5 |

MCASP3_AFSX |

MCASP11_AXR4 |

MCASP3_AXR2 |

13 |

~ |

~ |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

~ |

~ |

P8.39-P8.41¶

Pin |

P8.39 |

P8.40 |

P8.41 |

|---|---|---|---|

GPIO |

1 69 |

1 70 |

1 67 |

BALL |

AC26 |

AA24 |

AD29 |

REG |

0x00011C118 |

0x00011C11C |

0x00011C110 |

Page |

35 |

36 |

35 |

MODE 0 |

PRG0_PRU1_GPO6 |

PRG0_PRU1_GPO7 |

PRG0_PRU1_GPO4 |

1 |

PRG0_PRU1_GPI6 |

PRG0_PRU1_GPI7 |

PRG0_PRU1_GPI4 |

2 |

PRG0_RGMII2_RXC |

PRG0_IEP1_EDC_LATCH_IN1 |

PRG0_RGMII2_RX_CTL |

3 |

~ |

~ |

PRG0_PWM2_B2 |

4 |

RGMII4_RXC |

SPI3_CS0 |

RGMII4_RX_CTL |

5 |

RMII4_TXD0 |

~ |

RMII4_TXD1 |

6 |

~ |

MCAN11_TX |

~ |

7 |

GPIO0_69 |

GPIO0_70 |

GPIO0_67 |

8 |

GPMC0_A25 |

GPMC0_AD9 |

GPMC0_A24 |

9 |

~ |

~ |

~ |

10 |

~ |

~ |

~ |

11 |

~ |

~ |

~ |

12 |

MCASP1_AXR3 |

MCASP1_AXR4 |

MCASP1_AXR2 |

13 |

~ |

~ |

~ |

14 |

~ |

UART2_TXD |

~ |

Bootstrap |

~ |

~ |

~ |

P8.42-P8.44¶

Pin |

P8.42 |

P8.43 |

P8.44 |

|---|---|---|---|

GPIO |

1 68 |

1 65 |

1 66 |

BALL |

AB27 |

AD27 |

AC25 |

REG |

0x00011C114 |

0x00011C108 |

0x00011C10C |

Page |

35 |

34 |

35 |

MODE 0 |

PRG0_PRU1_GPO5 |

PRG0_PRU1_GPO2 |

PRG0_PRU1_GPO3 |

1 |

PRG0_PRU1_GPI5 |

PRG0_PRU1_GPI2 |

PRG0_PRU1_GPI3 |

2 |

~ |

PRG0_RGMII2_RD2 |

PRG0_RGMII2_RD3 |

3 |

~ |

PRG0_PWM2_A2 |

~ |

4 |

~ |

RGMII4_RD2 |

RGMII4_RD3 |

5 |

~ |

RMII4_CRS_DV |

RMII4_RX_ER |

6 |

~ |

~ |

~ |

7 |

GPIO0_68 |

GPIO0_65 |

GPIO0_66 |

8 |

GPMC0_AD8 |

GPMC0_A23 |

~ |

9 |

~ |

~ |

~ |

10 |

~ |

~ |

~ |

11 |

~ |

~ |

~ |

12 |

MCASP1_ACLKX |

MCASP1_ACLKR |

MCASP1_AFSR |

13 |

~ |

MCASP1_AXR10 |

MCASP1_AXR11 |

14 |

~ |

~ |

~ |

Bootstrap |

BOOTMODE6 |

~ |

~ |

P8.45-P8.46¶

Pin |

P8.45 |

P8.46 |

|---|---|---|

GPIO |

1 79 |

1 80 |

BALL |

AG29 |

Y25 |

REG |

0x00011C140 |

0x00011C144 |

Page |

38 |

38 |

MODE 0 |

PRG0_PRU1_GPO16 |

PRG0_PRU1_GPO17 |

1 |

PRG0_PRU1_GPI16 |

PRG0_PRU1_GPI17 |

2 |

PRG0_RGMII2_TXC |

PRG0_IEP1_EDC_SYNC_OUT1 |

3 |

PRG0_PWM1_A2 |

PRG0_PWM1_B2 |

4 |

RGMII4_TXC |

SPI3_CLK |

5 |

~ |

~ |

6 |

~ |

~ |

7 |

GPIO0_79 |

GPIO0_80 |

8 |

~ |

GPMC0_AD13 |

9 |

~ |

~ |

10 |

~ |

~ |

11 |

~ |

~ |

12 |

MCASP2_AXR2 |

MCASP2_AXR3 |

13 |

~ |

~ |

14 |

~ |

~ |

Bootstrap |

~ |

BOOTMODE3 |

Connector P9¶

The following tables show the pinout of the P9 expansion header. The SW is responsible for setting the default function of each pin. Refer to the processor documentation for more information on these pins and detailed descriptions of all of the pins listed. In some cases there may not be enough signals to complete a group of signals that may be required to implement a total interface.

The column heading is the pin number on the expansion header.

The GPIO row is the expected gpio identifier number in the Linux kernel.

Each row includes the gpiochipX and pinY in the format of X Y. You can use these values to directly control the GPIO pins with the commands shown below.

# to set the GPIO pin state to HIGH

debian@BeagleBone:~$ gpioset X Y=1

# to set the GPIO pin state to LOW

debian@BeagleBone:~$ gpioset X Y=0

For Example:

+---------+----------+

| Pin | P9.11 |

+=========+==========+

| GPIO | 1 1 |

+---------+----------+

Use the commands below for controlling this pin (P9.11) where X = 1 and Y = 1

# to set the GPIO pin state to HIGH

debian@BeagleBone:~$ gpioset 1 20=1

# to set the GPIO pin state to LOW

debian@BeagleBone:~$ gpioset 1 20=0

The BALL row is the pin number on the processor.

The REG row is the offset of the control register for the processor pin.

The MODE # rows are the mode setting for each pin. Setting each mode to align with the mode column will give that function on that pin.

If included, the 2nd BALL row is the pin number on the processor for a second processor pin connected to the same pin on the expansion header. Similarly, all row headings starting with 2nd refer to data for this second processor pin.

Important

DO NOT APPLY VOLTAGE TO ANY I/O PIN WHEN POWER IS NOT SUPPLIED TO THE BOARD. IT WILL DAMAGE THE PROCESSOR AND VOID THE WARRANTY.

NO PINS ARE TO BE DRIVEN UNTIL AFTER THE SYS_RESET LINE GOES HIGH.

P9.E1-P9.E4¶

E1 |

E2 |

E3 |

E4 |

|---|---|---|---|

USB1 DP |

USB1 DN |

VSYS_5V0 |

GND |

P9.01-P9.05¶

P9.01 |

P9.02 |

P9.03 |

P9.04 |

P9.05 |

|---|---|---|---|---|

GND |

GND |

VOUT_3V3 |

VOUT_3V3 |

VIN |

P9.06-P9.10¶

P9.06 |

P9.07 |

P9.08 |

P9.09 |

P9.10 |

|

|---|---|---|---|---|---|

VIN |

VOUT_SYS | VOUT_SYS |

RESET# |

RESET# |

||

P9.11-P9.13¶

Pin |

P9.11 |

P9.12 |

P9.13 |

|---|---|---|---|

GPIO |

1 1 |

1 45 |

1 2 |

BALL |

AC23 |

AE27 |

AG22 |

REG |

0x00011C004 |

0x00011C0B8 |

0x00011C008 |

Page |

39 |

29 |

40 |

MODE 0 |

PRG1_PRU0_GPO0 |

PRG0_PRU0_GPO2 |

PRG1_PRU0_GPO1 |

1 |

PRG1_PRU0_GPI0 |

PRG0_PRU0_GPI2 |

PRG1_PRU0_GPI1 |

2 |

PRG1_RGMII1_RD0 |

PRG0_RGMII1_RD2 |

PRG1_RGMII1_RD1 |

3 |

PRG1_PWM3_A0 |

PRG0_PWM2_A0 |

PRG1_PWM3_B0 |

4 |

RGMII1_RD0 |

RGMII3_RD2 |

RGMII1_RD1 |

5 |

RMII1_RXD0 |

RMII3_CRS_DV |

RMII1_RXD1 |

6 |

~ |

~ |

~ |

7 |

GPIO0_1 |

GPIO0_45 |

GPIO0_2 |

8 |

GPMC0_BE1n |

UART3_RXD |

GPMC0_WAIT0 |

9 |

RGMII7_RD0 |

~ |

RGMII7_RD1 |

10 |

~ |

~ |

~ |

11 |

~ |

~ |

~ |

12 |

MCASP6_ACLKX |

MCASP0_ACLKR |

MCASP6_AFSX |

13 |

~ |

~ |

~ |

14 |

UART0_RXD |

~ |

UART0_TXD |

Bootstrap |

~ |

~ |

~ |

P9.14-P9.16¶

Pin |

P9.14 |

P9.15 |

P9.16 |

|---|---|---|---|

GPIO |

1 93 |

1 47 |

1 94 |

BALL |

U27 |

AD25 |

U24 |

REG |

0x00011C178 |

0x00011C0C0 |

0x00011C17C |

Page |

56 |

30 |

56 |

MODE 0 |

RGMII5_RD3 |

PRG0_PRU0_GPO4 |

RGMII5_RD2 |

1 |

UART3_CTSn |

PRG0_PRU0_GPI4 |

UART3_RTSn |

2 |

~ |

PRG0_RGMII1_RX_CTL |

~ |

3 |

UART6_RXD |

PRG0_PWM2_B0 |

UART6_TXD |

4 |

VOUT1_DATA8 |

RGMII3_RX_CTL |

VOUT1_DATA9 |

5 |

TRC_DATA6 |

RMII3_TXD1 |

TRC_DATA7 |

6 |

EHRPWM2_A |

~ |

EHRPWM2_B |

7 |

GPIO0_93 |

GPIO0_47 |

GPIO0_94 |

8 |

GPMC0_A9 |

~ |

GPMC0_A10 |

9 |

~ |

~ |

~ |

10 |

~ |

~ |

~ |

11 |

~ |

~ |

~ |

12 |

MCASP11_AXR0 |

MCASP0_AXR2 |

MCASP11_AXR1 |

13 |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

P9.17-P9.18¶

Pin |

P9.17 |

~ |

P9.18 |

~ |

|---|---|---|---|---|

GPIO |

1 28 |

1 115 |

1 40 |

1 120 |

BALL |

AC21 |

AA3 |

AH22 |

Y2 |

REG |

0x00011C074 |

0x00011C1D0 |

0x00011C0A4 |

0x00011C1E4 |

Page |

49 |

67 |

53 |

68 |

MODE 0 |

PRG1_PRU1_GPO7 |

SPI0_D1 |

PRG1_PRU1_GPO19 |

SPI1_D1 |

1 |

PRG1_PRU1_GPI7 |

~ |

PRG1_PRU1_GPI19 |

~ |

2 |

PRG1_IEP1_EDC_LATCH_IN1 |

I2C6_SCL |

PRG1_IEP1_EDC_SYNC_OUT0 |

I2C6_SDA |

3 |

~ |

~ |

PRG1_PWM1_TZ_OUT |

~ |

4 |

SPI6_CS0 |

~ |

SPI6_D1 |

~ |

5 |

RMII6_RX_ER |

~ |

RMII6_TXD1 |

~ |

6 |

MCAN7_TX |

~ |

PRG1_ECAP0_IN_APWM_OUT |

~ |

7 |

GPIO0_28 |

GPIO0_115 |

GPIO0_40 |

GPIO0_120 |

8 |

~ |

~ |

~ |

PRG0_IEP1_EDC_SYNC_OUT0 |

9 |

~ |

~ |

~ |

~ |

10 |

VOUT0_DATA7 |

~ |

VOUT0_PCLK |

~ |

11 |

VPFE0_DATA15 |

~ |

~ |

~ |

12 |

MCASP4_AXR1 |

~ |

MCASP5_AXR1 |

~ |

13 |

~ |

~ |

~ |

~ |

14 |

UART3_TXD |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

~ |

P9.19-P9.20¶

Pin |

P9.19 |

~ |

P9.20 |

~ |

|---|---|---|---|---|

GPIO |

2 1 |

1 78 |

2 2 |

1 77 |

BALL |

W5 |

AF29 |

W6 |

AE25 |

REG |

0x00011C208 |

0x00011C13C |

0x00011C20C |

0x00011C138 |

Page |

19 |

38 |

19 |

37 |

MODE 0 |

MCAN0_RX |

PRG0_PRU1_GPO15 |

MCAN0_TX |

PRG0_PRU1_GPO14 |

1 |

~ |

PRG0_PRU1_GPI15 |

~ |

PRG0_PRU1_GPI14 |

2 |

~ |

PRG0_RGMII2_TX_CTL |

~ |

PRG0_RGMII2_TD3 |

3 |

~ |

PRG0_PWM1_B1 |

~ |

PRG0_PWM1_A1 |

4 |

I2C2_SCL |

RGMII4_TX_CTL |

I2C2_SDA |

RGMII4_TD3 |

5 |

~ |

~ |

~ |

~ |

6 |

~ |

~ |

~ |

~ |

7 |

GPIO1_1 |

GPIO0_78 |

GPIO1_2 |

GPIO0_77 |

8 |

~ |

~ |

~ |

~ |

9 |

~ |

~ |

~ |

~ |

10 |

~ |

~ |

~ |

~ |

11 |

~ |

~ |

~ |

~ |

12 |

~ |

MCASP2_AXR1 |

~ |

MCASP2_AXR0 |

13 |

~ |

~ |

~ |

~ |

14 |

~ |

UART2_RTSn |

~ |

UART2_CTSn |

Bootstrap |

~ |

~ |

~ |

~ |

P9.21-P9.22¶

Pin |

P9.21 |

~ |

P9.22 |

~ |

|---|---|---|---|---|

GPIO |

1 39 |

1 90 |

1 38 |

1 91 |

BALL |

AJ22 |

U28 |

AC22 |

U29 |

REG |

0x00011C0A0 |

0x00011C16C |

0x00011C09C |

0x00011C170 |

Page |

52 |

56 |

52 |

54 |

MODE 0 |

PRG1_PRU1_GPO18 |

RGMII5_TD0 |

PRG1_PRU1_GPO17 |

RGMII5_TXC |

1 |

PRG1_PRU1_GPI18 |

RMII7_TXD0 |

PRG1_PRU1_GPI17 |

RMII7_TX_EN |

2 |

PRG1_IEP1_EDC_LATCH_IN0 |

I2C3_SDA |

PRG1_IEP1_EDC_SYNC_OUT1 |

I2C6_SCL |

3 |

PRG1_PWM1_TZ_IN |

~ |

PRG1_PWM1_B2 |

~ |

4 |

SPI6_D0 |

VOUT1_DATA5 |

SPI6_CLK |

VOUT1_DATA6 |

5 |

RMII6_TXD0 |

TRC_DATA3 |

RMII6_TX_EN |

TRC_DATA4 |

6 |

PRG1_ECAP0_SYNC_IN |

EHRPWM1_A |

PRG1_ECAP0_SYNC_OUT |

EHRPWM1_B |

7 |

GPIO0_39 |

GPIO0_90 |

GPIO0_38 |

GPIO0_91 |

8 |

~ |

GPMC0_A6 |

~ |

GPMC0_A7 |

9 |

VOUT0_VP2_VSYNC |

~ |

VOUT0_VP2_DE |

~ |

10 |

VOUT0_VSYNC |

~ |

VOUT0_DE |

~ |

11 |

~ |

~ |

VPFE0_DATA10 |

~ |

12 |

MCASP5_AXR0 |

MCASP11_AFSX |

MCASP5_AFSX |

MCASP10_AXR2 |

13 |

~ |

~ |

~ |

~ |

14 |

VOUT0_VP0_VSYNC |

~ |

VOUT0_VP0_DE |

~ |

Bootstrap |

~ |

~ |

BOOTMODE1 |

~ |

P9.23-P9.25¶

Pin |

P9.23 |

P9.24 |

~ |

P9.25 |

~ |

|---|---|---|---|---|---|

GPIO |

1 10 |

1 119 |

1 13 |

1 127 |

1 104 |

BALL |

AG20 |

Y5 |

AJ24 |

AC4 |

W26 |

REG |

0x00011C028 |

0x00011C1E0 |

0x00011C034 |

0x00011C200 |

0x00011C1A4 |

Page |

42 |

68 |

43 |

69 |

54 |

MODE 0 |

PRG1_PRU0_GPO9 |

SPI1_D0 |

PRG1_PRU0_GPO12 |

UART1_CTSn |

RGMII6_RXC |

1 |

PRG1_PRU0_GPI9 |

UART5_RTSn |

PRG1_PRU0_GPI12 |

MCAN3_RX |

~ |

2 |

PRG1_UART0_CTSn |

I2C4_SCL |

PRG1_RGMII1_TD1 |

~ |

~ |

3 |

PRG1_PWM3_TZ_IN |

UART2_TXD |

PRG1_PWM0_A0 |

~ |

AUDIO_EXT_REFCLK2 |

4 |

SPI6_CS1 |

~ |

RGMII1_TD1 |

SPI2_D0 |

VOUT1_DE |

5 |

RMII5_RXD1 |

~ |

~ |

EQEP0_S |

TRC_DATA17 |

6 |

~ |

~ |

MCAN4_RX |

~ |

EHRPWM4_B |

7 |

GPIO0_10 |

GPIO0_119 |

GPIO0_13 |

GPIO0_127 |

GPIO0_104 |

8 |

GPMC0_ADVn_ALE |

PRG0_IEP1_EDC_LATCH_IN0 |

~ |

~ |

GPMC0_A20 |

9 |

PRG1_IEP0_EDIO_DATA_IN_OUT28 |

~ |

RGMII7_TD1 |

~ |

VOUT1_VP0_DE |

10 |

VOUT0_DATA23 |

~ |

VOUT0_DATA17 |

~ |

~ |

11 |

~ |

~ |

VPFE0_DATA1 |

~ |

~ |

12 |

MCASP3_ACLKX |

~ |

MCASP7_AFSX |

~ |

MCASP10_AXR7 |

13 |

~ |

~ |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

~ |

~ |

P9.26-P9.27¶

Pin |

P9.26 |

~ |

P9.27 |

~ |

|---|---|---|---|---|

GPIO |

1 118 |

1 12 |

1 46 |

1 124 |

BALL |

Y1 |

AF24 |

AD26 |

AB1 |

REG |

0x00011C1DC |

0x00011C030 |

0x00011C0BC |

0x00011C1F4 |

Page |

67 |

43 |

30 |

69 |

MODE 0 |

SPI1_CLK |

PRG1_PRU0_GPO11 |

PRG0_PRU0_GPO3 |

UART0_RTSn |

1 |

UART5_CTSn |

PRG1_PRU0_GPI11 |

PRG0_PRU0_GPI3 |

TIMER_IO7 |

2 |

I2C4_SDA |

PRG1_RGMII1_TD0 |

PRG0_RGMII1_RD3 |

SPI0_CS3 |

3 |

UART2_RXD |

PRG1_PWM3_TZ_OUT |

PRG0_PWM3_A2 |

MCAN2_TX |

4 |

~ |

RGMII1_TD0 |

RGMII3_RD3 |

SPI2_CLK |

5 |

~ |

~ |

RMII3_RX_ER |

EQEP0_B |

6 |

~ |

MCAN4_TX |

~ |

~ |

7 |

GPIO0_118 |

GPIO0_12 |

GPIO0_46 |

GPIO0_124 |

8 |

PRG0_IEP0_EDC_SYNC_OUT0 |

~ |

UART3_TXD |

~ |

9 |

~ |

RGMII7_TD0 |

~ |

~ |

10 |

~ |

VOUT0_DATA16 |

~ |

~ |

11 |

~ |

VPFE0_DATA0 |

~ |

~ |

12 |

~ |

MCASP7_ACLKX |

MCASP0_AFSR |

~ |

13 |

~ |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

~ |

P9.28-P9.29¶

Pin |

P9.28 |

~ |

P9.29 |

~ |

|---|---|---|---|---|

GPIO |

2 11 |

1 43 |

2 14 |

1 53 |

BALL |

U2 |

AF28 |

V5 |

AB25 |

REG |

0x00011C230 |

0x00011C0B0 |

0x00011C23C |

0x00011C0D8 |

Page |

18 |

29 |

68 |

31 |

MODE 0 |

ECAP0_IN_APWM_OUT |

PRG0_PRU0_GPO0 |

TIMER_IO1 |

PRG0_PRU0_GPO10 |

1 |

SYNC0_OUT |

PRG0_PRU0_GPI0 |

ECAP2_IN_APWM_OUT |

PRG0_PRU0_GPI10 |

2 |

CPTS0_RFT_CLK |

PRG0_RGMII1_RD0 |

OBSCLK0 |

PRG0_UART0_RTSn |

3 |

~ |

PRG0_PWM3_A0 |

~ |

PRG0_PWM2_B1 |

4 |

SPI2_CS3 |

RGMII3_RD0 |

~ |

SPI3_CS2 |

5 |

I3C0_SDAPULLEN |

RMII3_RXD1 |

~ |

PRG0_IEP0_EDIO_DATA_IN_OUT29 |

6 |

SPI7_CS0 |

~ |

SPI7_D1 |

MCAN10_RX |

7 |

GPIO1_11 |

GPIO0_43 |

GPIO1_14 |

GPIO0_53 |

8 |

~ |

~ |

~ |

GPMC0_AD4 |

9 |

~ |

~ |

~ |

~ |

10 |

~ |

~ |

~ |

~ |

11 |

~ |

~ |

~ |

~ |

12 |

~ |

MCASP0_AXR0 |

~ |

MCASP0_AFSX |

13 |

~ |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

BOOTMODE5 |

~ |

P9.30-P9.31¶

Pin |

P9.30 |

~ |

P9.31 |

~ |

|---|---|---|---|---|

GPIO |

2 13 |

1 44 |

2 12 |

1 52 |

BALL |

V6 |

AE28 |

U3 |

AB26 |

REG |

0x00011C238 |

0x00011C0B4 |

0x00011C234 |

0x00011C0D4 |

Page |

68 |

29 |

18 |

31 |

MODE 0 |

TIMER_IO0 |

PRG0_PRU0_GPO1 |

EXT_REFCLK1 |

PRG0_PRU0_GPO9 |

1 |

ECAP1_IN_APWM_OUT |

PRG0_PRU0_GPI1 |

SYNC1_OUT |

PRG0_PRU0_GPI9 |

2 |

SYSCLKOUT0 |

PRG0_RGMII1_RD1 |

~ |

PRG0_UART0_CTSn |

3 |

~ |

PRG0_PWM3_B0 |

~ |

PRG0_PWM3_TZ_IN |

4 |

~ |

RGMII3_RD1 |

~ |

SPI3_CS1 |

5 |

~ |

RMII3_RXD0 |

~ |

PRG0_IEP0_EDIO_DATA_IN_OUT28 |

6 |

SPI7_D0 |

~ |

SPI7_CLK |

MCAN10_TX |

7 |

GPIO1_13 |

GPIO0_44 |

GPIO1_12 |

GPIO0_52 |

8 |

~ |

~ |

~ |

GPMC0_AD3 |

9 |

~ |

~ |

~ |

~ |

10 |

~ |

~ |

~ |

~ |

11 |

~ |

~ |

~ |

~ |

12 |

~ |

MCASP0_AXR1 |

~ |

MCASP0_ACLKX |

13 |

~ |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

UART6_TXD |

Bootstrap |

BOOTMODE4 |

~ |

~ |

~ |

P9.32-P9.35¶

P9.32 |

P9.34 |

|---|---|

VDD_ADC |

GND |

Pin |

P9.33 |

~ |

P9.35 |

~ |

|---|---|---|---|---|

GPIO |

~ |

1 50 |

~ |

1 55 |

BALL |

K24 |

AC28 |

K29 |

AH27 |

REG |

0x00011C140 |

0x00011C0CC |

0x00011C148 |

0x00011C0E0 |

Page |

20 |

31 |

20 |

32 |

MODE 0 |

MCU_ADC0_AIN4 |

PRG0_PRU0_GPO7 |

MCU_ADC0_AIN6 |

PRG0_PRU0_GPO12 |

1 |

~ |

PRG0_PRU0_GPI7 |

~ |

PRG0_PRU0_GPI12 |

2 |

~ |

PRG0_IEP0_EDC_LATCH_IN1 |

~ |

PRG0_RGMII1_TD1 |

3 |

~ |

PRG0_PWM3_B1 |

~ |

PRG0_PWM0_A0 |

4 |

~ |

PRG0_ECAP0_SYNC_IN |

~ |

RGMII3_TD1 |

5 |

~ |

~ |

~ |

~ |

6 |

~ |

MCAN9_TX |

~ |

~ |

7 |

~ |

GPIO0_50 |

~ |

GPIO0_55 |

8 |

~ |

GPMC0_AD1 |

~ |

~ |

9 |

~ |

~ |

~ |

~ |

10 |

~ |

~ |

~ |

DSS_FSYNC0 |

11 |

~ |

~ |

~ |

~ |

12 |

~ |

MCASP0_AXR5 |

~ |

MCASP0_AXR8 |

13 |

~ |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

~ |

P9.36-P9.37¶

Pin |

P9.36 |

~ |

P9.37 |

~ |

|---|---|---|---|---|

GPIO |

~ |

1 56 |

~ |

1 57 |

BALL |

K27 |

AH29 |

K28 |

AG28 |

REG |

0x00011C144 |

0x00011C0E4 |

0x00011C138 |

0x00011C0E8 |

Page |

20 |

32 |

20 |

32 |

MODE 0 |

MCU_ADC0_AIN5 |

PRG0_PRU0_GPO13 |

MCU_ADC0_AIN2 |

PRG0_PRU0_GPO14 |

1 |

~ |

PRG0_PRU0_GPI13 |

~ |

PRG0_PRU0_GPI14 |

2 |

~ |

PRG0_RGMII1_TD2 |

~ |

PRG0_RGMII1_TD3 |

3 |

~ |

PRG0_PWM0_B0 |

~ |

PRG0_PWM0_A1 |

4 |

~ |

RGMII3_TD2 |

~ |

RGMII3_TD3 |

5 |

~ |

~ |

~ |

~ |

6 |

~ |

~ |

~ |

~ |

7 |

~ |

GPIO0_56 |

~ |

GPIO0_57 |

8 |

~ |

~ |

~ |

UART4_RXD |

9 |

~ |

~ |

~ |

~ |

10 |

~ |

DSS_FSYNC2 |

~ |

~ |

11 |

~ |

~ |

~ |

~ |

12 |

~ |

MCASP0_AXR9 |

~ |

MCASP0_AXR10 |

13 |

~ |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

~ |

P9.38-P9.39¶

Pin |

P9.38 |

~ |

P9.39 |

~ |

|---|---|---|---|---|

GPIO |

~ |

1 58 |

~ |

1 54 |

BALL |

L28 |

AG27 |

K25 |

AJ28 |

REG |

0x00011C13C |

0x00011C0EC |

0x00011C130 |

0x00011C0DC |

Page |

~ |

33 |

20 |

32 |

MODE 0 |

MCU_ADC0_AIN3 |

PRG0_PRU0_GPO15 |

MCU_ADC0_AIN0 |

PRG0_PRU0_GPO11 |

1 |

~ |

PRG0_PRU0_GPI15 |

~ |

PRG0_PRU0_GPI11 |

2 |

~ |

PRG0_RGMII1_TX_CTL |

~ |

PRG0_RGMII1_TD0 |

3 |

~ |

PRG0_PWM0_B1 |

~ |

PRG0_PWM3_TZ_OUT |

4 |

~ |

RGMII3_TX_CTL |

~ |

RGMII3_TD0 |

5 |

~ |

~ |

~ |

~ |

6 |

~ |

~ |

~ |

~ |

7 |

~ |

GPIO0_58 |

~ |

GPIO0_54 |

8 |

~ |

UART4_TXD |

~ |

~ |

9 |

~ |

~ |

~ |

CLKOUT |

10 |

~ |

DSS_FSYNC3 |

~ |

~ |

11 |

~ |

~ |

~ |

~ |

12 |

~ |

MCASP0_AXR11 |

~ |

MCASP0_AXR7 |

13 |

~ |

~ |

~ |

~ |

14 |

~ |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

~ |

P9.40-P9.42¶

Pin |

P9.40 |

~ |

P9.41 |

P9.42 |

~ |

|---|---|---|---|---|---|

GPIO |

~ |

1 81 |

2 0 |

1 123 |

1 18 |

BALL |

K26 |

AA26 |

AD5 |

AC2 |

AJ21 |

REG |

0x00011C134 |

0x00011C148 |

0x00011C204 |

0x00011C1F0 |

0x00011C04C |

Page |

20 |

38 |

69 |

68 |

45 |

MODE 0 |

MCU_ADC0_AIN1 |

PRG0_PRU1_GPO18 |

UART1_RTSn |

UART0_CTSn |

PRG1_PRU0_GPO17 |

1 |

~ |

PRG0_PRU1_GPI18 |

MCAN3_TX |

TIMER_IO6 |

PRG1_PRU0_GPI17 |

2 |

~ |

PRG0_IEP1_EDC_LATCH_IN0 |

~ |

SPI0_CS2 |

PRG1_IEP0_EDC_SYNC_OUT1 |

3 |

~ |

PRG0_PWM1_TZ_IN |

~ |

MCAN2_RX |

PRG1_PWM0_B2 |

4 |

~ |

SPI3_D0 |

SPI2_D1 |

SPI2_CS0 |

~ |

5 |

~ |

~ |

EQEP0_I |

EQEP0_A |

RMII5_TXD1 |

6 |

~ |

MCAN12_TX |

~ |

~ |

MCAN5_TX |

7 |

~ |

GPIO0_81 |

GPIO1_0 |

GPIO0_123 |

GPIO0_18 |

8 |

~ |

GPMC0_AD14 |

~ |

~ |

~ |

9 |

~ |

~ |

~ |

~ |

~ |

10 |

~ |

~ |

~ |

~ |

~ |

11 |

~ |

~ |

~ |

~ |

VPFE0_DATA6 |

12 |

~ |

MCASP2_AFSX |

~ |

~ |

MCASP3_AXR3 |

13 |

~ |

~ |

~ |

~ |

~ |

14 |

~ |

UART2_RXD |

~ |

~ |

~ |

Bootstrap |

~ |

~ |

~ |

~ |

~ |

P9.43-P9.46¶

P9.43 |

P9.44 |

P9.45 |

P9.46 |

|---|---|---|---|

GND |

GND |

GND |

GND |

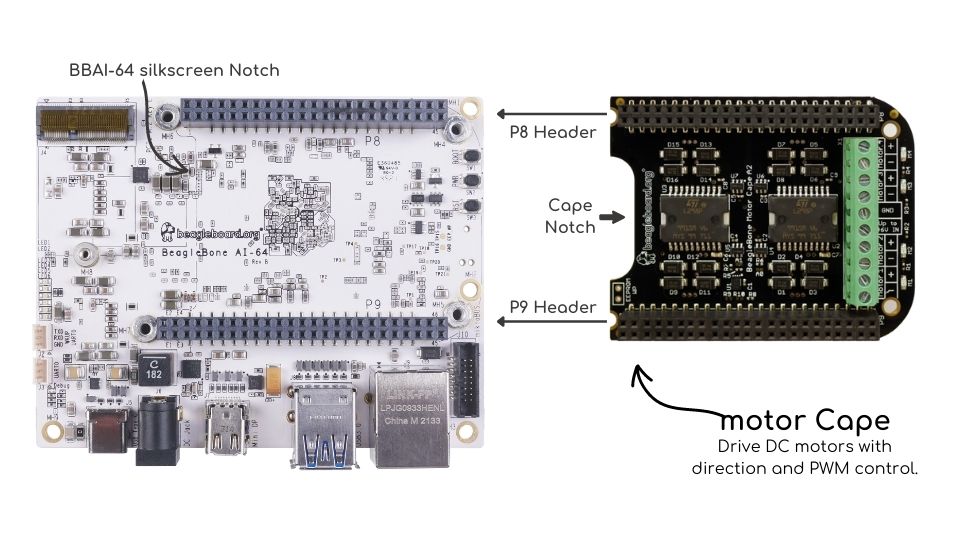

Cape Board Support¶

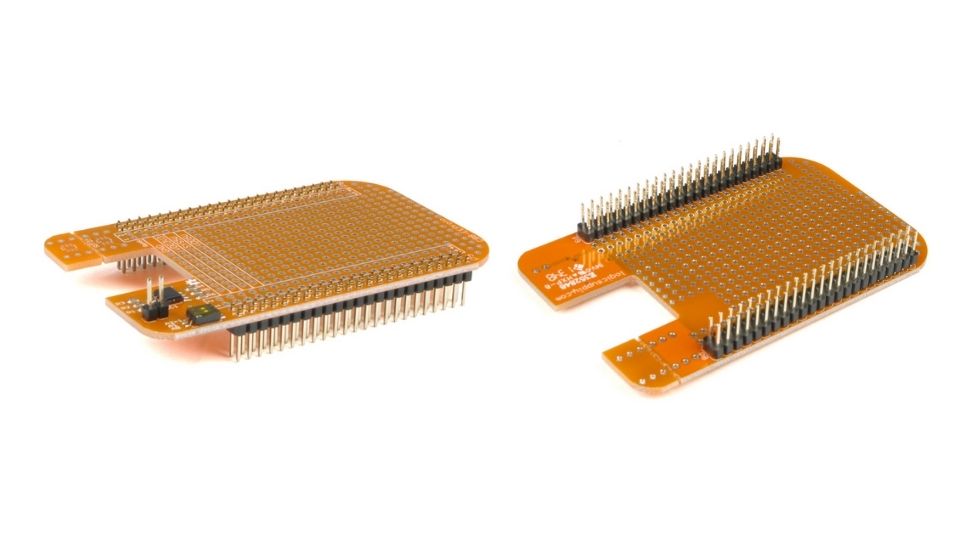

BeagleBone AI-64 has the ability to accept up to four EEPROM addressable expansion boards or capes stacked onto the expansion headers. The word cape comes from the shape of the expansion board for BeagleBone boards as it is fitted around the Ethernet connector on the main board. For BeagleBone this notch acts as a key to ensure proper orientation of the cape. On AI-64 you can see a clear silkscreen marking for the cape orientation. Most of BeagleBone capes can be used with your BeagleBone AI-64 also like shown in BeagleBone AI-64 cape placement below.

Fig. 77 BeagleBone AI-64 cape placement¶

This section describes the rules & guidelines for creating capes to ensure proper operation with BeagleBone AI-64 and proper interoperability with other capes that are intended to coexist with each other. Co-existence is not a requirement and is in itself, something that is impossible to control or administer. But, people will be able to create capes that operate with other capes that are already available based on public information as it pertains to what pins and features each cape uses. This information will be able to be read from the EEPROM on each cape.

For those wanting to create their own capes this should not put limits on the creation of capes and what they can do, but may set a few basic rules that will allow the software to administer their operation with BeagleBone AI-64. For this reason there is a lot of flexibility in the specification that we hope most people will find it liberating in the spirit of Open Source Hardware. On the other hand we are sure that there are others who would like to see tighter control, more details, more rules and much more order to the way capes are handled.

Over time, this specification will change and be updated, so please refer to the latest version of this manual prior to designing your own capes to get the latest information.

Warning

Do not apply voltage to any I/O pin when power is not supplied to the board. It will damage the processor and void the warranty.

BeagleBone AI-64 Cape Compatibility¶

The expansion headers on BeagleBone Black and BeagleBone AI-64 provides similar pin configuration options on P8 and P9 expansion header pins thus provide cape compatibility to a certain extent. Which means most BeagleBone Black capes will also be compatible with BeeagleBone AI-64.

See BeagleBone cape interface spec for compatibility information.

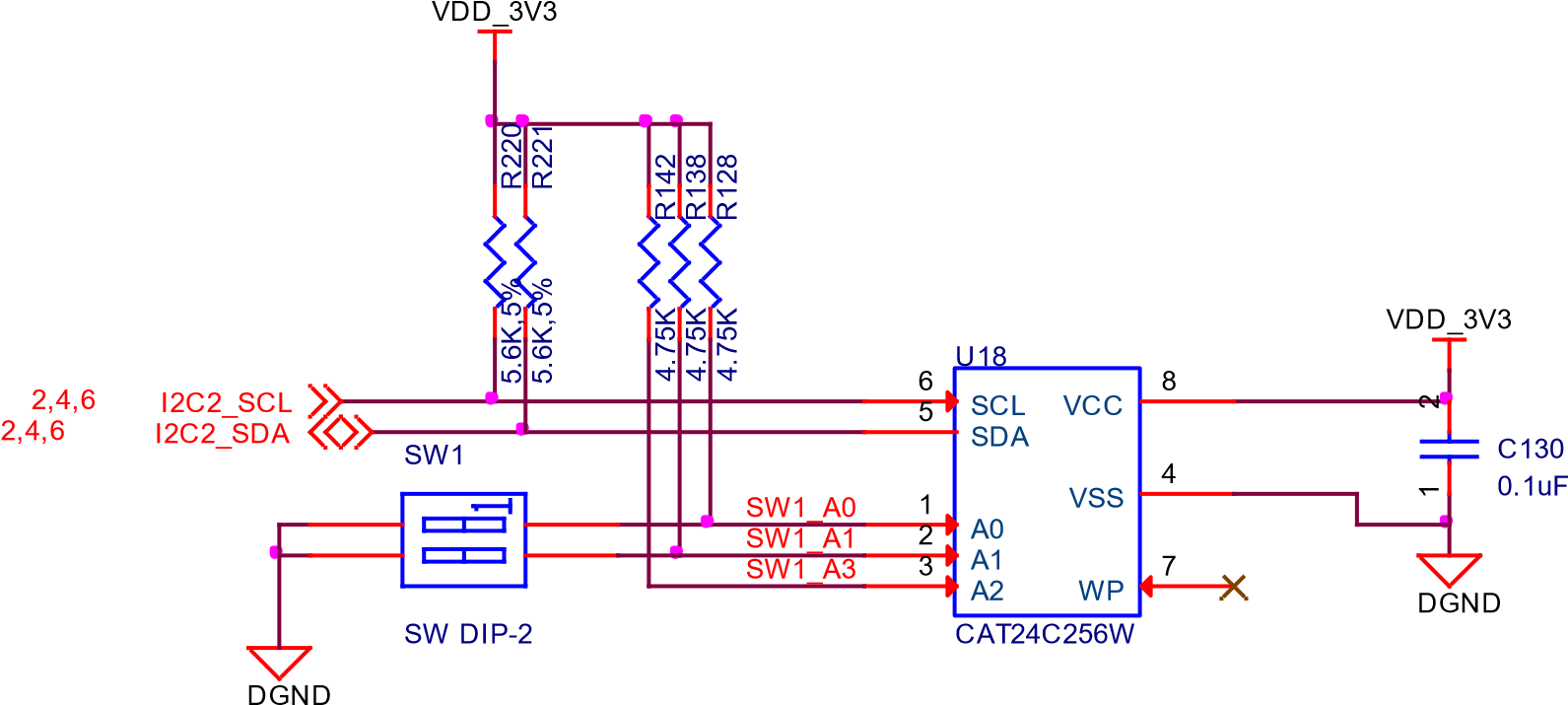

EEPROM¶

Each cape must have its own EEPROM containing information that will allow the software to identify the board and to configure the expansion headers pins during boot as needed. The one exception is proto boards intended for prototyping. They may or may not have an EEPROM on them. An EEPROM is required for all capes sold in order for them operate correctly when plugged into BeagleBone AI-64.

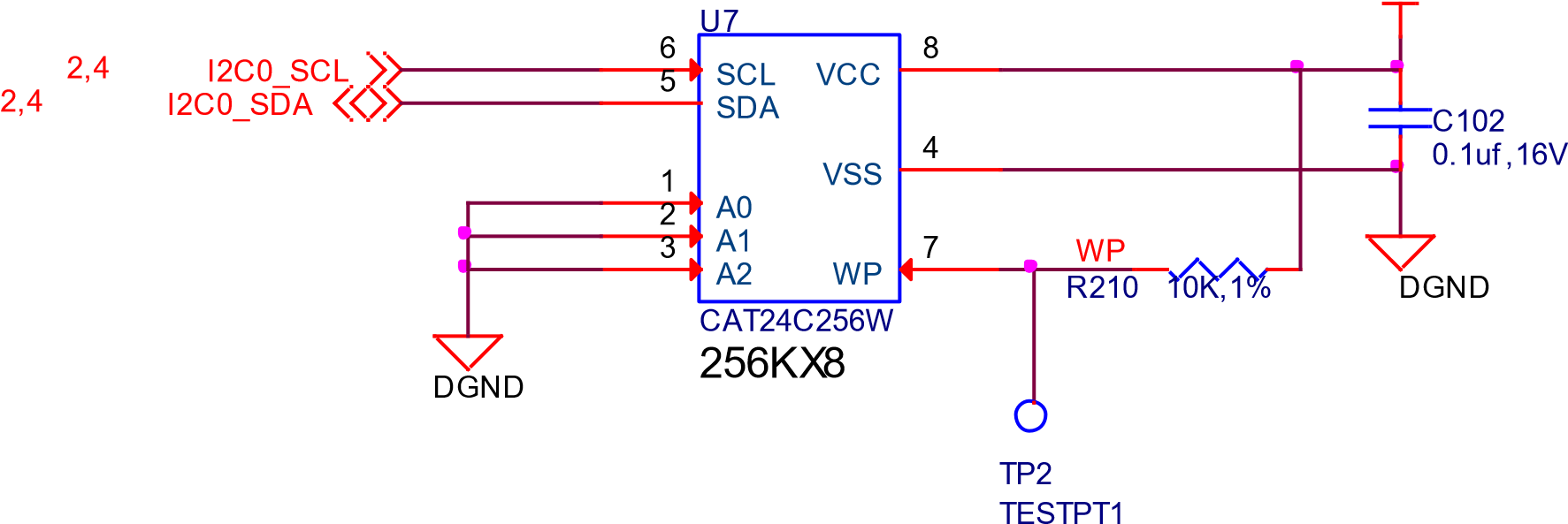

The address of the EEPROM will be set via either jumpers or a dipswitch on each expansion board. Expansion board EEPROM without write protect below is the design of the EEPROM circuit.

Fig. 78 Expansion board EEPROM without write protect¶

The addressing of this device requires two bytes for the address which is not used on smaller size EEPROMs, which only require only one byte. Other compatible devices may be used as well. Make sure the device you select supports 16 bit addressing. The part package used is at the discretion of the cape designer.

EEPROM Address¶

In order for each cape to have a unique address, a board ID scheme is used that sets the address to be different depending on the setting of the dipswitch or jumpers on the capes. A two position dipswitch or jumpers is used to set the address pins of the EEPROM.

It is the responsibility of the user to set the proper address for each board and the position in the stack that the board occupies has nothing to do with which board gets first choice on the usage of the expansion bus signals. The process for making that determination and resolving conflicts is left up to the SW and, as of this moment in time, this method is a something of a mystery due to the new Device Tree methodology introduced in the 3.8 kernel.

Address line A2 is always tied high. This sets the allowable address range for the expansion cards to 0x54 to**0x57**. All other I2C addresses can be used by the user in the design of their capes. But, these addresses must not be used other than for the board EEPROM information. This also allows for the inclusion of EEPROM devices on the cape if needed without interfering with this EEPROM. It requires that A2 be grounded on the EEPROM not used for cape identification.

I2C Bus¶

The EEPROMs on each expansion board are connected to I2C2 on connector P9 pins 19 and 20. For this reason I2C2 must always be left connected and should not be changed by SW to remove it from the expansion header pin mux settings. If this is done, the system will be unable to detect the capes.

The I2C signals require pullup resistors. Each board must have a 5.6K resistor on these signals. With four capes installed this will result in an effective resistance of 1.4K if all capes were installed and all the resistors used were exactly 5.6K. As more capes are added the resistance is reduced to overcome capacitance added to the signals. When no capes are installed the internal pullup resistors must be activated inside the processor to prevent I2C timeouts on the I2C bus.

The I2C2 bus may also be used by capes for other functions such as I/O expansion or other I2C compatible devices that do not share the same address as the cape EEPROM.

EEPROM Write Protect¶

The design in Expansion board EEPROM with write protect has the write protect disabled. If the write protect is not enabled, this does expose the EEPROM to being corrupted if the I2C2 bus is used on the cape and the wrong address written to. It is recommended that a write protection function be implemented and a Test Point be added that when grounded, will allow the EEPROM to be written to. To enable write operation, Pin 7 of the EEPROM must be tied to ground.

When not grounded, the pin is HI via pullup resistor R210 and therefore write protected. Whether or not Write Protect is provided is at the discretion of the cape designer.

Todo

Variable & MAC Memory

VSYS_IO_3V3

Fig. 79 Expansion board EEPROM with write protect¶

EEPROM Data Format¶

Expansion Board EEPROM shows the format of the contents of the expansion board EEPROM. Data is stored in Big Endian with the least significant value on the right. All addresses read as a single byte data from the EEPROM, but two byte addressing is used. ASCII values are intended to be easily read by the user when the EEPROM contents are dumped.

Todo

Clean/Update table

Name |

Offset |

Size (bytes) |

Contents |

|---|---|---|---|

Header |

0 |

4 |

0xAA, 0x55, 0x33, 0xEE |

EEPROM Revision |

4 |

2 |

Revision number of the overall format of this EEPROM in ASCII =A1 |

Board Name |

6 |

32 |

Name of board in ASCII so user can read it when the EEPROM is dumped. Up to developer of the board as to what they call the board.. |

Version |

38 |

4 |

Hardware version code for board in ASCII.Version format is up to the developer.i.e. 02.1…00A1….10A0 |

Manufacturer |

42 |

16 |

ASCII name of the manufacturer. Company or individual’s name. |

Part Number |

58 |

16 |

ASCII Characters for the part number. Up to maker of the board. |

Number of Pins |

74 |

2 |

Number of pins used by the daughter board including the power pins used. Decimal value of total pins 92 max, stored in HEX. |

Serial Number |

76 |

12 |

Serial number of the board. This is a 12 character string which is: WWYY&&&&nnnn where, WW = 2 digit week of the year of production, YY = 2 digit year of production , &&&&=Assembly code to let the manufacturer document the assembly number or product. A way to quickly tell from reading the serial number what the board is. Up to the developer to determine. nnnn = incrementing board number for that week of production |

Pin Usage |

88 |

148 |

Two bytes for each configurable pins of the 74 pins on the expansion connectors, MSB LSB Bit order: 15..14 ….. 1..0 Bit 15….Pin is used or not…0=Unused by cape 1=Used by cape Bit 14-13…Pin Direction…..1 0=Output 01=Input 11=BDIR Bits 12-7…Reserved……..should be all zeros Bit 6….Slew Rate …….0=Fast 1=Slow Bit 5….Rx Enable…….0=Disabled 1=Enabled Bit 4….Pull Up/Dn Select….0=Pulldown 1=PullUp Bit 3….Pull Up/DN enabled…0=Enabled 1=Disabled Bits 2-0 …Mux Mode Selection…Mode 0-7 |

VDD_3V3B Current |

236 |

2 |

Maximum current in milliamps. This is HEX value of the current in decimal 1500mA=0x05 0xDC 325mA=0x01 0x45 |

VDD_5V Current |

238 |

2 |

Maximum current in milliamps. This is HEX value of the current in decimal 1500mA=0x05 0xDC 325mA=0x01 0x45 |

SYS_5V Current |

240 |

2 |

Maximum current in milliamps. This is HEX value of the current in decimal 1500mA=0x05 0xDC 325mA=0x01 0x45 |

DC Supplied |

242 |

2 |

Indicates whether or not the board is supplying voltage on the VDD_5V rail and the current rating 000=No 1-0xFFFF is the current supplied storing the decimal quivalent in HEX format |

Available |

244 |

32543 |

Available space for other non-volatile codes/data to be used as needed by the manufacturer or SW driver. Could also store presets for use by SW. |

Todo

Align with other boards and migrate away from pin usage entries for BeagleBone Black expansion

Pin Usage Consideration¶

This section covers things to watch for when hooking up to certain pins on the expansion headers.

Expansion Connectors¶

A combination of male and female headers is used for access to the expansion headers on the main board. There are three possible mounting configurations for the expansion headers:

Single -no board stacking but can be used on the top of the stack.

Stacking-up to four boards can be stacked on top of each other.

Stacking with signal stealing-up to three boards can be stacked on top of each other, but certain boards will not pass on the signals they are using to prevent signal loading or use by other cards in the stack.

The following sections describe how the connectors are to be implemented and used for each of the different configurations.

Non-Stacking Headers-Single Cape¶

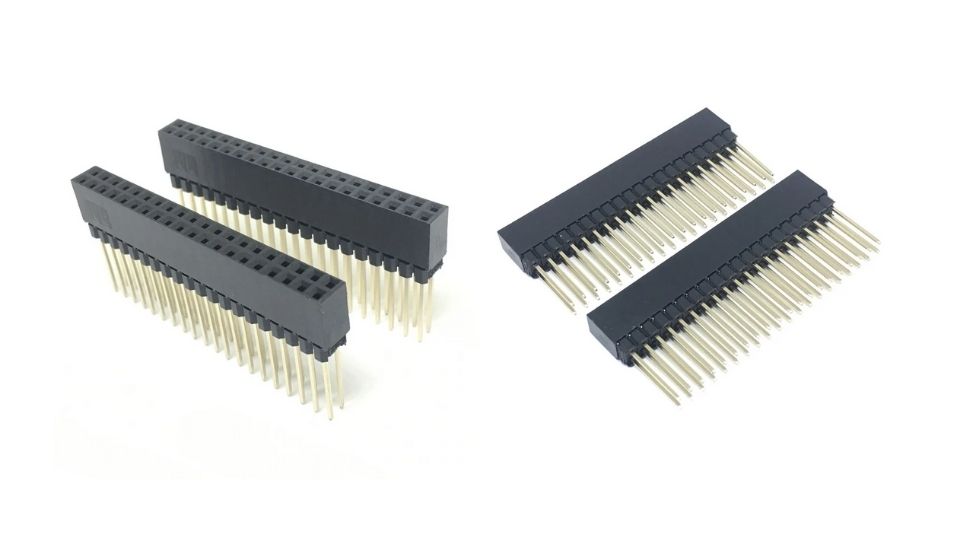

For non-stacking capes single configurations or where the cape can be the last board on the stack, the two 46 pin expansion headers use the same connectors. Single expansion connector is a picture of the connector. These are dual row 23 position 2.54mm x 2.54mm connectors.

Fig. 80 Single expansion connector¶

The connector is typically mounted on the bottom side of the board as shown in Single cape expansion connector on BeagleBone Proto Cape with EEPROM from onlogic . These are very common connectors and should be easily located. You can also use two single row 23 pin headers for each of the dual row headers.

Fig. 81 Single cape expansion connector on BeagleBone Proto Cape with EEPROM from onlogic¶

It is allowed to only populate the pins you need. As this is a non-stacking configuration, there is no need for all headers to be populated. This can also reduce the overall cost of the cape. This decision is up to the cape designer.

For convenience listed in Single Cape Connectors are some possible choices for part numbers on this connector. They have varying pin lengths and some may be more suitable than others for your use. It should be noted, that the longer the pin and the further it is inserted into BeagleBone AI-64 connector, the harder it will be to remove due to the tension on 92 pins. This can be minimized by using shorter pins or removing those pins that are not used by your particular design. The first item in**Table 18** is on the edge and may not be the best solution. Overhang is the amount of the pin that goes past the contact point of the connector on BeagleBone AI-64

SUPPLIER |

PARTNUMBER |

LENGTH(in) |

OVERHANG(in) |

|---|---|---|---|

TSHC-123-D-03-145-G-LF |

.145 |

.004 |

|

TSHC-123-D-03-240-G-LF |

.240 |

.099 |

|

TSHC-123-D-03-255-G-LF |

.255 |

.114 |

The G in the part number is a plating option. Other options may be used as well as long as the contact area is gold. Other possible sources are Sullins and Samtec for these connectors. You will need to ensure the depth into the connector is sufficient

Main Expansion Headers-Stacking¶

For stacking configuration, the two 46 pin expansion headers use the same connectors. Expansion Connector is a picture of the connector. These are dual row 23 position 2.54mm x 2.54mm connectors.

Fig. 82 Expansion Connector¶

The connector is mounted on the top side of the board with longer tails to allow insertion into BeagleBone AI-64. Stacked cape expansion connector is the connector configuration for the connector.

Fig. 83 Stacked cape expansion connector¶

For convenience listed in Table 18 are some possible choices for part numbers on this connector. They have varying pin lengths and some may be more suitable than others for your use. It should be noted, that the longer the pin and the further it is inserted into BeagleBone AI-64 connector, the harder it will be to remove due to the tension on 92 pins. This can be minimized by using shorter pins. There are most likely other suppliers out there that will work for this connector as well. If anyone finds other suppliers of compatible connectors that work, let us know and they will be added to this document. The first item in Table 19 is on the edge and may not be the best solution. Overhang is the amount of the pin that goes past the contact point of the connector on BeagleBone AI-64.

The third part listed in Stacked Cape Connectors will have insertion force issues.

SUPPLIER |

PARTNUMBER |

TAIL LENGTH(in) |

OVERHANG(in) |

|---|---|---|---|

SSHQ-123-D-06-G-LF |

.190 |

0.049 |

|

SSHQ-123-D-08-G-LF |

.390 |

0.249 |

|

SSHQ-123-D-10-G-LF |

.560 |

0.419 |

There are also different plating options on each of the connectors above. Gold plating on the contacts is the minimum requirement. If you choose to use a different part number for plating or availability purposes, make sure you do not select the “LT” option.

Other possible sources are Sullins and Samtec but make sure you select one that has the correct mating depth.

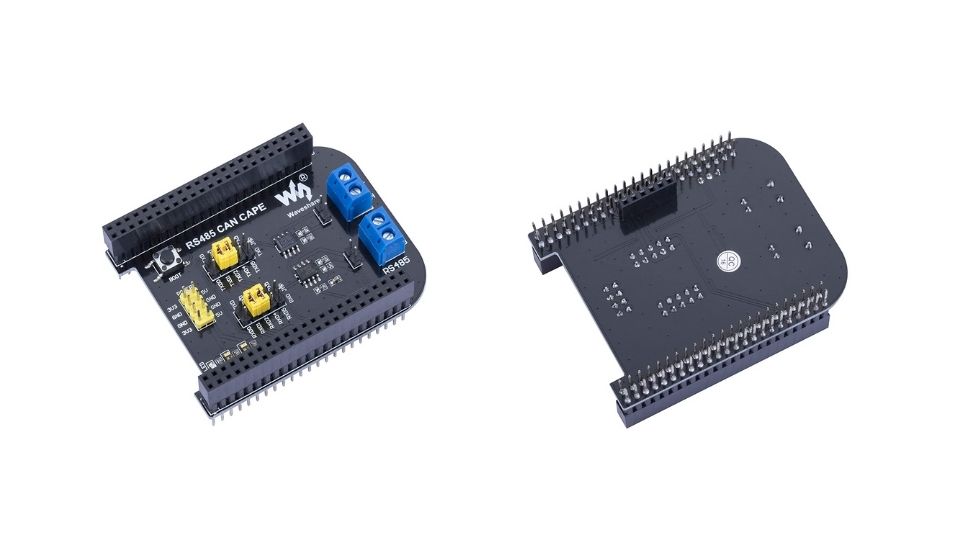

Stacked Capes w/Signal Stealing¶

Stacked with signal stealing expansion connector figure is the connector configuration for stackable capes that does not provide all of the signals upwards for use by other boards. This is useful if there is an expectation that other boards could interfere with the operation of your board by exposing those signals for expansion. This configuration consists of a combination of the stacking and nonstacking style connectors.

Fig. 84 Stacked with signal stealing expansion connector figure¶

Retention Force¶

The length of the pins on the expansion header has a direct relationship to the amount of force that is used to remove a cape from BeagleBone AI-64. The longer the pins extend into the connector the harder it is to remove. There is no rule that says that if longer pins are used, that the connector pins have to extend all the way into the mating connector on BeagleBone AI-64, but this is controlled by the user and therefore is hard to control. We have also found that if you use gold pins, while more expensive, it makes for a smoother finish which reduces the friction.

This section will attempt to describe the tradeoffs and things to consider when selecting a connector and its pin length.

BeagleBone AI-64 Female Connectors¶

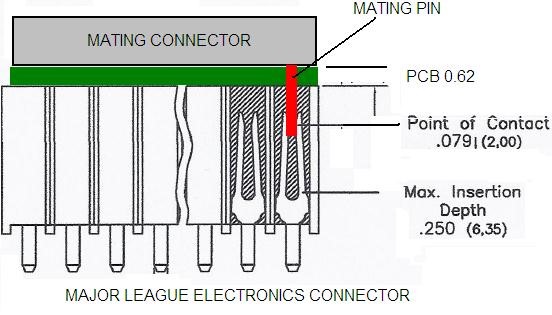

Connector Pin Insertion Depth shows the key measurements used in calculating how much the pin extends past the contact point on the connector, what we call overhang.

Fig. 85 Connector Pin Insertion Depth¶

To calculate the amount of the pin that extends past the Point of Contact, use the following formula:

Overhang=Total Pin Length- PCB thickness (.062) - contact point (.079)

The longer the pin extends past the contact point, the more force it will take to insert and remove the board. Removal is a greater issue than the insertion.

Signal Usage¶

Based on the pin muxing capabilities of the processor, each expansion pin can be configured for different functions. When in the stacking mode, it will be up to the user to ensure that any conflicts are resolved between multiple stacked cards. When stacked, the first card detected will be used to set the pin muxing of each pin. This will prevent other modes from being supported on stacked cards and may result in them being inoperative.

In Cape Header Connectors section of this document, the functions of the pins are defined as well as the pin muxing options. Refer to this section for more information on what each pin is. To simplify things, if you use the default name as the function for each pin and use those functions, it will simplify board design and reduce conflicts with other boards.

Interoperability is up to the board suppliers and the user. This specification does not specify a fixed function on any pin and any pin can be used to the full extent of the functionality of that pin as enabled by the processor.

DO NOT APPLY VOLTAGE TO ANY I/O PIN WHEN POWER IS NOT SUPPLIED TO THE BOARD. IT WILL DAMAGE THE PROCESSOR AND VOID THE WARRANTY.

NO PINS ARE TO BE DRIVEN UNTIL AFTER THE SYS_RESET LINE GOES HIGH.

Cape Power¶

This section describes the power rails for the capes and their usage.

Main Board Power¶

The Expansion Voltages describes the voltages from the main board that are available on the expansion connectors and their ratings. All voltages are supplied by connector**P9**. The current ratings listed are per pin.

Current |

Name |

P9 |

P9 |

Name |

Current |

|---|---|---|---|---|---|

250mA |

VDD_3V3B |

3 |

4 |

VDD_3V3B |

250mA |

1000mA |

VDD_5V |

5 |

6 |

VDD_5V |

1000mA |

250mA |

SYS_5V |

7 |

8 |

SYS_5V |

250mA |

The VSYS_IO_3V3 rail is supplied by the LDO on BeagleBone AI-64 and is the primary power rail for expansion boards. If the power requirement for the capes exceeds the current rating, then locally generated voltage rail can be used. It is recommended that this rail be used to power any buffers or level translators that may be used.

DC_VDD_5V is the main power supply from the DC input jack. This voltage is not present when the board is powered via USB. The amount of current supplied by this rail is dependent upon the amount of current available. Based on the board design, this rail is limited to 1A per pin from the main board.

The VSYS_5V0 rail is the main rail for the regulators on the main board. When powered from a DC supply or USB, this rail will be 5V. The available current from this rail depends on the current available from the USB and DC external supplies.

Expansion Board External Power¶

A cape can have a jack or terminals to bring in whatever voltages may be needed by that board. Care should be taken not to let this voltage be fed back into any of the expansion header pins.

It is possible to provide 5V to the main board from an expansion board. By supplying a 5V signal into the DC_VDD_5V rail, the main board can be supplied. This voltage must not exceed 5V. You should not supply any voltage into any other pin of the expansion connectors. Based on the board design, this rail is limited to 1A per pin to BeagleBone AI-64.

There are several precautions that need to be taken when working with the expansion headers to prevent damage to the board.

Do not apply any voltages to any I/O pins when the board is not powered on.

Do not drive any external signals into the I/O pins until after the VSYS_IO_3V3 rail is up.

Do not apply any voltages that are generated from external sources.

If voltages are generated from the DC_VDD_5V signal, those supplies must not become active until after the VSYS_IO_3V3 rail is up.

If you are applying signals from other boards into the expansion headers, make sure you power the board up after you power up the BeagleBone AI-64 or make the connections after power is applied on both boards.

Powering the processor via its I/O pins can cause damage to the processor.

Todo

Add BeagleBone AI-64 cape mechanical characteristics**

Standard Cape Size¶

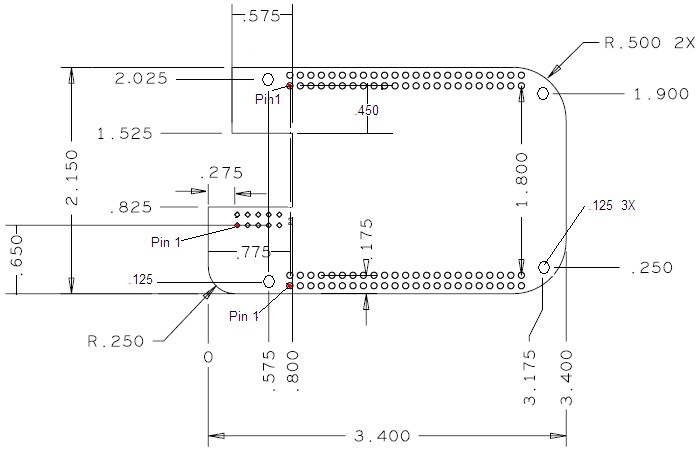

Cape board dimensions shows the outline of the standard cape. The dimensions are in inches.

Fig. 86 Cape board dimensions¶

A notch is provided for BeagleBone Ethernet connector to stick up higher than the cape when mounted. This also acts as a key function to ensure that the cape is oriented correctly. Space is also provided to allow access to the user LEDs and reset button on BeagleBone board. On BeagleBone AI-64 board align it with the notch on the board silkscreen.

Extended Cape Size¶

Capes larger than the standard board size are also allowed. A good example would be the new BeagleBone AI-64 robotics cape. There is no practical limit to the sizes of these types of boards. The notch is also optional, but it is up to the supplier to ensure that the cape is not plugged incorrectly on BeagleBone AI-64 such that damage would be cause to BeagleBone AI-64. Any such damage will be the responsibility of the supplier of such a cape to repair. As with all capes, the EEPROM is required and compliance with the power requirements must be adhered to.

RANDOM PRU STUFF THAT MIGHT NEED A HOME¶

Note

I don’t want to blow this information away until I know no work went into it for TDA4VM. It is probably just AM3358 or AM5729 information. :-(

PRU0 and PRU1 Access below shows which PRU-ICSS signals can be accessed on the BeagleBone AI-64 and on which connector and pins they are accessible from. Some signals are accessible on the same pins.

PIN |

PROC |

NAME |

||||

|---|---|---|---|---|---|---|

P8 |

11 |

R12 |

GPIO1_13 |

pr1_pru0_pru_r30_15 (Output) |

||

12 |

T12 |

GPIO1_12 |

pr1_pru0_pru_r30_14 (Output) |

|||

15 |

U13 |

GPIO1_15 |

pr1_pru0_pru_r31_15 (Input) |

|||

16 |

V13 |

GPIO1_14 |

pr1_pru0_pru_r31_14 (Input) |

|||

20 |

V9 |

GPIO1_31 |

pr1_pru1_pru_r30_13 (Output) |

pr1_pru1_pru_r31_13 (INPUT) |

||

21 |

U9 |

GPIO1_30 |

pr1_pru1_pru_r30_12 (Output) |

pr1_pru1_pru_r31_12 (INPUT) |

||

27 |

U5 |

GPIO2_22 |

pr1_pru1_pru_r30_8 (Output) |

pr1_pru1_pru_r31_8 (INPUT) |

||

28 |

V5 |

GPIO2_24 |

pr1_pru1_pru_r30_10 (Output) |

pr1_pru1_pru_r31_10 (INPUT) |

||

29 |

R5 |

GPIO2_23 |

pr1_pru1_pru_r30_9 (Output) |

pr1_pru1_pru_r31_9 (INPUT) |

||

39 |

T3 |

GPIO2_12 |

pr1_pru1_pru_r30_6 (Output) |

pr1_pru1_pru_r31_6 (INPUT) |

||

40 |

T4 |

GPIO2_13 |

pr1_pru1_pru_r30_7 (Output) |

pr1_pru1_pru_r31_7 (INPUT) |

||

41 |

T1 |

GPIO2_10 |

pr1_pru1_pru_r30_4 (Output) |

pr1_pru1_pru_r31_4 (INPUT) |

||

42 |

T2 |

GPIO2_11 |

pr1_pru1_pru_r30_5 (Output) |

pr1_pru1_pru_r31_5 (INPUT) |

||

43 |

R3 |

GPIO2_8 |

pr1_pru1_pru_r30_2 (Output) |

pr1_pru1_pru_r31_2 (INPUT) |

||

44 |

R4 |

GPIO2_9 |

pr1_pru1_pru_r30_3 (Output) |

pr1_pru1_pru_r31_3 (INPUT) |

||

45 |

R1 |

GPIO2_6 |

pr1_pru1_pru_r30_0 (Output) |

pr1_pru1_pru_r31_0 (INPUT) |

||

46 |

R2 |

GPIO2_7 |

pr1_pru1_pru_r30_1 (Output) |

pr1_pru1_pru_r31_1 (INPUT) |

||

P9 |

17 |

A16 |

I2C1_SCL |

pr1_uart0_txd |

||

18 |

B16 |

I2C1_SDA |

pr1_uart0_rxd |

|||

19 |

D17 |

I2C2_SCL |

pr1_uart0_rts_n |

|||

20 |

D18 |

I2C2_SDA |

pr1_uart0_cts_n |

|||

21 |

B17 |

UART2_TXD |

pr1_uart0_rts_n |

|||

22 |

A17 |

UART2_RXD |

pr1_uart0_cts_n |

|||

24 |

D15 |

UART1_TXD |

pr1_uart0_txd |

pr1_pru0_pru_r31_16 (Input) |

||

25 |

A14 |

GPIO3_21footnote:[GPIO3_21 is also the 24.576MHZ clock input to the processor to enable HDMI audio. To use this pin the oscillator must be disabled.] |

pr1_pru0_pru_r30_5 (Output) |

pr1_pru0_pru_r31_5 (Input) |

||

26 |

D16 |

UART1_RXD |

pr1_uart0_rxd |

pr1_pru1_pru_r31_16 |

||

27 |

C13 |

GPIO3_19 |

pr1_pru0_pru_r30_7 (Output) |

pr1_pru0_pru_r31_7 (Input) |

||

28 |

C12 |

SPI1_CS0 |

eCAP2_in_PWM2_out |

pr1_pru0_pru_r30_3 (Output) |

pr1_pru0_pru_r31_3 (Input) |

|

29 |

B13 |

SPI1_D0 |

pr1_pru0_pru_r30_1 (Output) |

pr1_pru0_pru_r31_1 (Input) |

||

30 |

D12 |

SPI1_D1 |

pr1_pru0_pru_r30_2 (Output) |

pr1_pru0_pru_r31_2 (Input) |

||

31 |

A13 |

SPI1_SCLK |

pr1_pru0_pru_r30_0 (Output) |

pr1_pru0_pru_r31_0 (Input) |